“在6月初的北京媒体见面会上,德州仪器无线基站业务部总经理Kathy Brown女士宣布推出了面向通信基础局端设备的新型多核SoC架构,其中包括针对无线基站的4核芯片,以及媒体网关和网络应用的8核芯片。

”在6月初的北京媒体见面会上,德州仪器无线基站业务部总经理Kathy Brown女士宣布推出了面向通信基础局端设备的新型多核SoC架构,其中包括针对无线基站的4核芯片,以及媒体网关和网络应用的8核芯片。这一新架构采用了40nm工艺;处理器主频为1.2GHz,运算能力为256GMACS/128GFLOPS;在单芯片上可同时支持定点和浮点运算;针对新兴标准的可编程平台;软件具有兼容性和可扩展性,可用同一个软件开发宏、微、毫微微基站。

现今,无线网络数据的增长对通信基础局端设备产生了许多新的需求:一是降低功耗。基站设备是7天24小时运行的,能源消耗较大,白天繁忙时与晚上相对空闲时对功率的要求不同;二是异构网络。因存在不同形式的基站,大大小小的基站;三是需要MIMO功能、优化的矩阵处理环境的接收机;四是频谱效率要高;五是投资成本与运营成本的降低。正是基于这样的趋势和挑战,TI开发了面向通信基础局端设备的新型多核SoC架构。

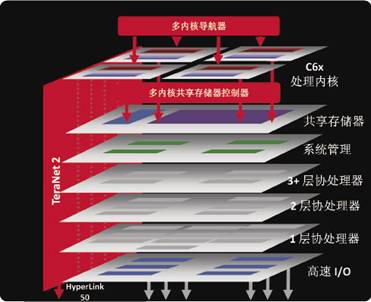

Kathy Brown女士介绍说,新SoC采用C6x内核,无线基站层1、层2、层3协处理器,和丰富的独立片内连接层的技术。此外更重要的是TI有支持无线基站领先的技术:多核导航器,它支持内核与存储器存取之间的直接通信,从而解放外设存取,充分释放多核性能;片上交换架构――TeraNet2,其速度高达2Mb/s,可为所有SoC组成部分提供高带宽和低时延互连;多核共享存储器控制器,可使内核直接访问存储器,无需穿过TeraNet2,可加快片上及外接存储器存取速度;HyperLink50,提供芯片级互连,可跨越多个芯片。

Kathy Brown女士进一步指出,TI提供芯片的同时,在开发工具上也投入了很多。一方面为客户带来了业界效率最高的编译器,因而能够提供更高价值的产品;另一方面还提供调试工具的支持,使开发人员能够深入到程序的具体执行内部发现问题、找出问题。可实现跨越式起步的软件也是TI为客户开发的产品,该软件提供最底层操作系统和一些通用模块,如GSM模块、LTE模块以及音视频处理模块,这样可以使客户把自己的研发关注在差异化应用开发上。

对于市场对TI芯片的认可情况,Kathy Brown表示,目前TI每个季度有关WCDMA的芯片发货量基本上都超过100万片,第1代器件(采用90nm工艺)和第2代器件(采用60nm工艺)的出货量都超过了100万片。这些出货器件50% 以上用于无外部ASIC或FPGA的WCDMA 1 层与2 层。此外Kathy Brown还提到,TI PHY软件已经被全球超过200多家运营商所使用,包括GSM/EDGE、WiMAX、WCDMA以及最新开发的LTE技术。今年2月推出以来,基于新型多内核、多层SoC 架构的产品系列已经在全球被超过40多项设计采用,其中仅基于新型架构的4 核基站器件就有20 多项设计被采纳,这些设计有的是在样片还没有出来之前就被设计进去了,这可以看出TI芯片的被认可度。

多内核SoC架构

分享到:

猜你喜欢