Ў°IDT НЖіцТөҪзКЧёцОӘұгРҜКҪПы·СУҰУГУЕ»ҜөДҝЙұаіМөН№ҰәДјЖКұЖчјю

Ўұ

IDTНЖіцIDT VersaClockјЖКұПөБРЖчјюЧоРВІъЖ·5P49EE801Ўў5P49EE802Ўў5P49EE601Ўў5P49EE602 әН 5P49EE502ЎЈVersaClockөН№ҰәДЖчјюКЗТ»ЦЦҝЙұаіМКұЦУЙъіЙЖчЈ¬ЧЁОӘөзіШ№©өзөДПы·СУҰУГЙијЖЈ¬°ьАЁЦЗДЬКЦ»ъЎўёцИЛөјәҪЙиұёЎўMP3 ІҘ·ЕЖчЎўЙгПс»ъәНЖдЛыКЦіЦУҰУГЈ¬ТФҪөөН№ҰәДәНУЕ»ҜөзВ·°еІјҫЦЎЈ

РВөДјЖКұЖчјюҝЙПФЦшҪөөН№ҰәДЈ¬ВъЧгПы·СөзЧУЙиұёІ»¶ПФціӨөД№ҰВКР§ВКРиЗуЎЈVersaClock өН№ҰәДЖчјюНЁ№эҪ«Т»ёцКұЦУКдіцөД№ҰВКРиЗуҙУ 30-40mW јхЙЩөҪ 4-8mWЈ¬СУіӨДҝЗ°ұгРҜКҪөзЧУІъЖ·өДөзіШКЩГьЎЈVersaClock өН№ҰәДҪвҫц·Ҫ°ё»№ҙуҙуҪөөНБЛКЎөзДЈКҪЈЁ20ҰМWЈ©әН32kHz КұЦУЦч¶ҜЛҜГЯДЈКҪЈЁ200ҰМWЈ©өДөзБҰПыәДЈ¬ХвР©¶јКЗРРТөРВөДөН№ҰәД»щЧјЎЈVersaClock өН№ҰәДЖчјюТСҝӘКј№©»хЎЈ

5P49EEЎБІъЖ·МШРФ

• 5ёцРВөДVersaClockөН№ҰәДЖчјю¶јУР4ёцДЪІҝЛшПа»·Ј¬Гҝёц¶јҝЙ¶АБўұаіМІўДЬЙъіЙ4ЦЦ¶АУРЖөВКЈ¬УРЦъУЪУЕ»ҜГҝёцКұЦУКдіцөДРФДЬәНМбёЯПөНіҫ«И·¶ИЈ»

• ОӘБЛ°пЦъЙијЖИЛФұМбёЯБй»оРФЈ¬ЖөВКҝЙТФУЙКұЦУКдИлЎўТ»ёцОВ¶ИІ№іҘҫ§МеХсөҙЖчЈЁTCXOЈ©»т»щұҫДЈКҪҫ§МеІОҝјЙъіЙЎЈК№УГТ»ёцІОҝјКұЦУФКРнЙијЖИЛФұјт»ҜЙијЖЈ¬ІўФЪұЈіЦҫ«И·¶ИөДН¬КұҪЪКЎөзВ·°еҝХјдЈ»

• 4ёцДЪІҝЛшПа»·ЦРөД1ёцЦ§іЦА©ЖөЙъіЙЈ¬ТФјхЙЩөзҙЕёЙИЕЈЁEMIЈ©Ј¬Хв¶ФВъЧгFCCөИИПЦӨТӘЗуКЗұШРиөДЈ»

• РВ VersaClock ЖчјюҝЙТФЙъіЙ 5kHz өҪ 120MHz өДЖөВКЈ¬КөПЦұгРҜКҪПы·СУҰУГёьҙуөДЙијЖБй»оРФЈ»

• ХвР©Жчјю»№јжИЭ¶аЦЦІ»Н¬өДКдіцАаРНЎӘЎӘҙУөҘ¶Л LVCMOS өҪІо·Ц VLDSЈ¬УГТ»ёцЖчјюЦ§іЦІ»Н¬АаРНөДјЖКұПөНіЈ¬јт»ҜЙијЖәНУЕ»ҜөзВ·°еІјҫЦЈ»

• 20ТэҪЕәН24ТэҪЕЛД·ҪұвЖҪОЮТэПЯЈЁQFNЈ©·вЧ°ЎЈ

ПкЗйјыЈәwww.idt.com

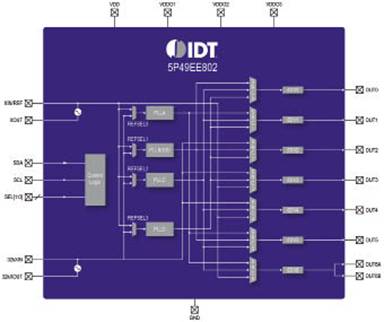

5P49EE802јЬ№№Нј

GEC

·ЦПнөҪЈә

ІВДгПІ»¶