IC技术讲座是本刊2005年推出的全新技术类栏目。为了让工程师在设计开发中完善和拓展基础理论与系统知识,丰富应用经验,《世界电子元器件》和bwin客户端

联合清华大学等知名院校共同创办了这个栏目,特约知名学者、教授以及著名半导体公司的应用工程师撰写,以系列讲座的方式对热点IC技术进行全面而系统的介绍,涵盖最新技术要点。最先开设的讲座将围绕三大课题:DSP、FPGA和嵌入式系统,每个课题都将连载6期。

概述

在目前的很多数字系统设计中,FPGA等可编程逻辑器件并不是其中的主要部件,仅作为粘附逻辑或实现一定具体功能的处理模块,协助电路板上的其他ASIC或处理器共同完成系统功能。

随着微电子、EDA以及其他相关技术的不断发展,FPGA等可编程逻辑器件的资源和功能也越来越丰富,设计也越来越方便,很多FPGA器件中已经能够嵌入多种处理器核和复杂的逻辑模块,从而可以灵活高效地实现更多功能和接口,并在复杂的数字系统设计中发挥越来越重要的作用。

本文介绍了FPGA器件的一些高级应用,以及在FPGA设计中可能使用到的开发工具。

FPGA高级应用

所有FPGA器件厂商和相关的EDA软件公司都在努力将FPGA发展成为设计灵活方便、功能丰富强大的基础硬件,并在其上实现系统级、平台级的复杂数字系统设计与实现。

目前,除了作为粘附逻辑和一般功能模块的实现器件,很多FPGA都可以实现更多高级的功能,所以也就涉及到了FPGA的高级应用和开发,这里仅简要介绍下面几个方面的内容:可编程片上系统与嵌入式系统、高性能数字信号处理系统、可重配置计算系统、基于网络的可重配置技术、IP核的开发与复用技术。随着技术的进步和需求的发展,这方面的内容必将逐步普及,并不断得到扩充。

可编程片上系统与嵌入式系统

把整个数字系统或整个系统的数字部分实现在一块可编程逻辑器件芯片上,就构成了可编程片上系统(SOPC)。SOPC是一种比较特殊的嵌入式系统:它不仅是一个由单个芯片完成系统的主要逻辑功能的片上系统(SOC),更重要的,它是一个可编程的系统,结合了SOC和FPGA的优势,设计、实现、扩展、升级都非常灵活方便,并且具有软硬件在系统可编程的能力。

在FPGA上实现可编程片上系统,一般包含嵌入式处理器核、其他功能模块以及相应的接口电路,要求FPGA具有丰富的可编程逻辑资源,具有一定容量的片内存储器,具有较灵活的调试接口,以及丰富的IP核资源。具体设计中将涉及到嵌入式系统设计的各方面技术内容,包括处理器、嵌入式操作系统、高速电路设计等等。另外,由于主要的逻辑设计是在FPGA上进行,因此还涉及到软硬件协同设计和仿真技术。

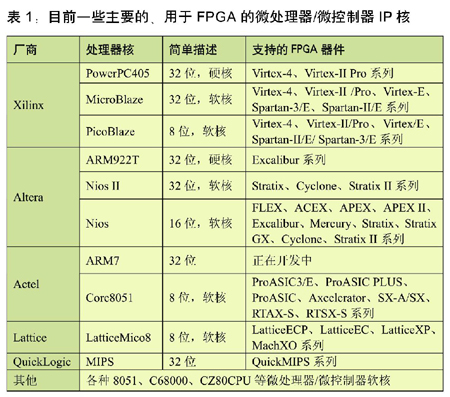

集成了硬核或软核CPU、DSP、存储器、外围I/O及可编程逻辑模块的SOPC,在设计和应用的灵活性以及成本方面有较大的优势。为了实现SOPC,国际上著名的现场可编程逻辑器件厂商如Altera、Xilinx等都在不断努力,开发适于系统集成的新器件和开发工具,这又进一步促进了SOPC的发展。目前一些常见的处理器核如表1所示。

高性能数字信号处理系统

数字信号处理(DSP)已经广泛应用于消费电子、汽车、国防等领域。多媒体信息处理、雷达信号处理、软件无线电等应用都要求系统具有极高的数字信号处理能力。这种需求不仅导致数字信号处理器的不断改进,也推动了FPGA、AISC等硬件解决方案的发展。

FPGA能够高效地实现多种DSP应用。目前在数字通信、网络、视频和图像等应用领域,FPGA已经成为数字信号处理系统的核心器件。除了查找表和寄存器,很多FPGA芯片中还具有多个专为高性能DSP而设计的硬件乘法器、加法器单元、高速输入/输出接口,甚至包含DSP专用的逻辑单元。这些硬件资源与片内的分布式存储器、块状存储器、处理器核、可编程逻辑可以高速互连,为用户提供高性能的DSP处理能力。

FPGA所具有的大规模并行处理能力和可编程的灵活性使得DSP系统设计能获得极高的处理性能,并且能够适应日益变化的标准、协议和性能需求。相对于高端DSP处理器,使用FPGA可以提高集成度,降低系统成本。Xilinx、Altera等公司提供的高性能FPGA器件、IP核、嵌入处理器,已经成为DSP应用的高效替代方案,采用基于Matlab的系统级设计方式,使用方便。因此,对FPGA和硬件描述语言不熟悉的设计者可以使用Matlab/Simulink以及FPGA厂商提供的软件工具进行基于FPGA的DSP设计。

另外,主要的FPGA厂商和第三方IP设计公司都在提供越来越多的DSP IP核,利用这些资源,设计者可以将精力集中在高层次设计上,无需关心底层模块的实现细节,缩短开发周期,减小开发成本。

可重配置计算系统

可重配置计算又称为自适应计算,是一种新型的、介于ASIC和通用处理器之间的计算模式,这种计算模式同时具有硬件的灵活性和软件的可编程性,可以配置各种系统实现的模式和参数,包括:处理器个数、互连机制、存储器容量与使用模式、外部设备与接口、高级语言编程、操作系统支持等等。

这种计算结构的硬件一般由多个可重配置的功能单元、处理器和互连结构组成。FPGA是目前可重配置计算硬件中的关键部件,它可以很容易的通过重新下载配置信息来改变功能,这样就可以将多项工作利用同一个FPGA芯片以时分复用的方式分别完成,用较小规模的FPGA芯片实现更大规模的数字系统。

更重要的是,可重配置逻辑可以配置成不同的功能,从而为不同的应用和计算提供硬件支持。因此可重配置计算要求硬件具有动态可重配置的能力,即能够实时更新FPGA器件的全部或部分逻辑。在对部分逻辑功能进行更新时,不影响期间中其他逻辑单元的正常工作。因此,FPGA器件的动态可重配置能力是可重配置计算的实现基础,目前少量高端的FPGA芯片能够在一定程度上支持动态可重配置。

基于网络的可重配置逻辑

基于网络的可重配置逻辑,其中网络主要指的是Internet,也可以是无线网络、电话网络、或其他的网络连接机制。基于Internet的可重配置逻辑(Internet

Reconfigurable Logic,IRL)是Xilinx倡导的一种新的FPGA设计理念,这种技术的核心是通过Internet对远程设备的硬件设计和软件程序进行升级、重构、调试和监控。

一般来说,IRL功能应该具有如下功能:网络接入功能(包括硬件接口和协议栈)、网络数据交换功能、FPGA配置功能(可能需支持JTAG模式)、故障恢复功能等等。在嵌入式Internet技术和处理器的支持下,这些功能目前已经可以实现,甚至可以使用FPGA内嵌的处理器核来实现。

设备厂商可以通过Internet访问远程目标机,通过HTTP、FTP等网络协议实现数据、文件传输和交互控制的功能。从而实现设备或产品的远程监控、调试、维护、修复、升级等操作。

采用IRL技术将给设备厂商带来几个好处:缩短产品上市时间、减少产品维护费用、延长产品生命周期。随着嵌入式系统和Internet技术的蓬勃发展,这种设计理念必将对嵌入式设备的设计模式产生深远的影响。

IP核的开发与复用

数字系统一般由多个功能模块构成,其中很多模块是通用的,FPGA和EDA厂商预先设计调试好这些通用单元,构成具有自主知识产权的功能模块,称之为IP(Intellectual

Property)核。IP核的开发和复用技术是FPGA高级应用的技术基础和强有力的支持。

IP复用技术是指在设计过程中,通过继承、共享或购买所需的IP核,然

后再利用EDA工具进行设计、综合和验证,从而加速系统的设计过程,降低开发风险。由于系统设计复杂性的提高以及上市时间方面的压力,设计者不断寻求有效的设计方法,以缩短设计周期,提高设计效率。使用大容量FPGA进行复杂数字系统设计时,采用IP核复用技术是十分必要的,并且正在逐渐成为系统设计的重要手段,从而缩短设计周期和上市时间,降低风险,减小投入,提高系统的性能和可靠性。

IP核是IP复用的载体和核心内容,对于不同的应用需求、协议规范和行业标准,IP核也涵盖了处理器、外设控制器、DSP算法等多个方面。为了使IP核易于使用,其设计必须遵循一定的规范和准则。许多研究和开发组织不仅开发了许多IP核,还编写了详细的IP核编码风格和项目模板,并倡导使用标准的互连机制,规范各种IP核的接口标准。

FPGA开发工具

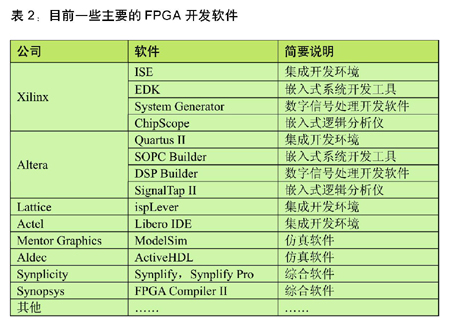

FPGA开发工具包括软件工具和硬件工具两种。其中硬件工具主要是FPGA厂商或第三方厂商开发的FPGA开发板及其下载线,另外还包括示波器、逻辑分析仪等板级的调试仪器。在软件方面,针对FPGA设计的各个阶段,FPGA厂商和EDA软件公司提供了很多优秀的EDA工具。如何充分利用各种工具的特点,如何进行多种EDA工具的协同设计,对FPGA的开发非常重要。充分利用各种EDA工具的优点,能够提高系统性能和开发效率。FPGA开发可能使用的软件工具如表2所示。

在FPGA设计的各个环节都有不同公司提供不同的EDA工具。每种EDA工具都有自己的特点。一般由FPGA厂商提供的集成开发环境,如Altera

Quartus II和Xilinx ISE,在逻辑综合和设计仿真环节都不是非常优秀,因此一般都会提供第三方EDA工具的接口,让用户更方便地利用其他EDA工具。为了提高设计效率,优化设计结果,很多厂家提供了各种专业软件,用以配合CPLD/FPGA芯片厂家提供的工具进行更高效的设计。比较常见的使用方式是:FPGA厂商提供的集成开发环境、专业逻辑仿真软件、专业逻辑综合软件一起使用,进行多种EDA工具的协同设计。比如Quartus

II+ModelSim+FPGA Compiler II,ISE+ModelSim+Synplify Pro等等。

Xilinx、Altera、Lattice、Actel这几个主要的FPGA厂商都推出了各自FPGA器件的集成开发环境软件,并且都在自己的开发软件中为一些第三方软件预留接口。其他EDA厂商为这些FPGA厂商提供各自产品的定制版本,比如Mentor

Graphics公司的逻辑仿真软件ModelSim、Aldel公司的逻辑仿真软件ActiveHDL、Synplicity公司的逻辑综合工具Synplify

Pro、Synopsys公司的逻辑综合工具FPGA Compiler II等等。

总结

目前,低成本、高性能的FPGA器件正在不断推向市场,为复杂数字系统的实现提供了一个灵活高效的硬件基础,随着可编程逻辑器件工艺的不断进步,FPGA内部硬件资源将越来越丰富,处理能力将越来越高,IP核的种类和性能也将不断发展,使FPGA真正成为数字系统设计的平台。

另外,随着FPGA开发软件能力的不断增强,设计者可以方便的使用高层次的系统描述语言完成软硬件协同设计和模块化设计,而软/硬件功能分配和底层硬件实现都由EDA软件自动完成,从而大幅度提高系统的设计效率。

随着科学技术和市场需求的发展,FPGA等可编程逻辑器件必将更加广泛的应用在各个领域。SOPC、可重配置计算、IP核复用、IRL等设计理念以及功能强大的EDA工具将会对设计方式产生新的变革,也将给产品带来新的创意和更丰富的功能。

|