摘要

对于复杂的系统,鲁棒性是非常重要的。为了协助客户建立鲁棒性系统,KeyStone器件提供了多种硬件保护机制,如内存保护、EDC。本文介绍如何利用这些特性在KeyStone器件上建立一个鲁棒的系统。同时提供了与文档配套的例程。

1 简介

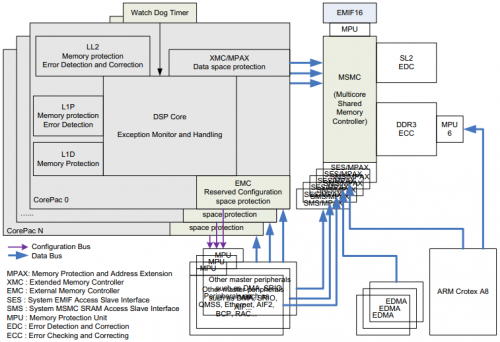

如图1所示,KeyStone器件提供了多种协助客户建立鲁棒性应用的特性。

图1 KeyStone器件鲁棒系统

如图1所示,在LL2、L1P及L1D中集成了内存保护模块;LL2、SL2及DDR控制器中集成了错误检查纠正模块;L1P 集成了错误检测模块。MPAX和MPU模块附在总线上,用于监控检测以避免非法的总线访问。每个DSP CorePac有一个独立的MPAX用于监控与MSMC连接的总线。

对于系统中其他的master,根据权限ID进行分类。对每个权限ID,在MSMC中集成了2个MPAX用于监视与该权限ID 相关的访问。其中一个是SES MPAX 用于保护对DDR3的访问,另一个是SMS MPAX 用于保护对SL2的访问。关于每个master对应的权限ID,参考相应的器件手册。

某些外设的配置端口上添加了MPU,用于保护对该外设配置区域的非法访问。但是并非所有的外设都受MPU的保护,具体参考相应器件手册中受MPU保护的外设列表。每个CorePac有一个看门狗定时器用于监视其活动,如果该核死机,看门狗可以触发不可屏蔽中断或者复位信号。

EMC可以避免DSP core访问没有映射的的配置空间,XMC则可以避免DSP core访问没有映射的数据空间。所有这些功能都由硬件模块实现,使用这些功能对系统性能基本上没有影响。使用EDC会对存储器的访问性能稍有影响,但从整个系统层面上看,它几乎是微不足道的。

在出现问题时,所有这些模块可以向DSP core触发异常,DSP core的异常监控模块可以记录这些状态并触发异常服务程序执行相应的操作。本文讨论这些特性的应用,并给出相关基于寄存器层CSL 实现的例程。代码使用如下方式定义寄存器指针。

上述各种特性具体描述分布于各自子系统的文档中,本文最后的参考章节中列出了所有相关的文档。在看本文之前,假设客户已经阅读了相关属性对应的文档,所以本文旨在提供相关的补充信息。

本文适用于KeyStone 1系列DSP,例程在TCI6614 EVM,C6670 EVM,C6678 EVM上进行了验证。对于其他的KeyStone器件包扩KeyStone 2系列,基本功能都是一样的,一些细节上的些许差异请参阅相应器件手册。

2 内存保护

文档“Memory Protection On KeyStone Devices(SPRWIKI9012)”中讨论了KeyStone器件上的内存保护属性,其中包括其它文档中没有的很多有用信息,本节在其基础上做一些总结和补充。

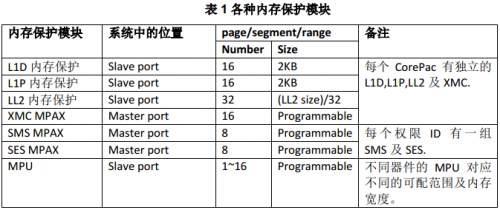

表1 总结列出不同内存保护模块的差异。

系统中有多个master和slave,位于slave输入端口的保护模块用于阻止来自其他master对该slave的非法访问;位于master输出端口的保护模块用于阻止该master对所有其他slave的非法访问。每个内存页、分片或范围的保护属性都是可编程的。

2.1 L1及LL2内存保护

关于L1及LL2内存保护的基本信息参考“TMS320C66x CorePac User Guide(SPUGW0)”中内存保护章节。

L1及LL2内存保护只区分7个外部请求ID,但是系统可能有16个权限ID。默认情况下,系统权限ID 0~5映射到CorePac AID 0~5,所有其他的权限ID均映射到AIDx。

CorePac AID与系统权限ID之间的映射关系可由EMC编程配置,具体参考“TMS320C66x CorePac User Guide(SPUGW0)”中“外部存储控制器(EMC)”章节。注意,IDMA的AID与其所属CorePac的数值一致,EDMA传输的权限ID与配置并发起这个传输的核的编号一致。

通常L1被配置为cache,此时所有L1相关的内存保护属性寄存器应该清零从而阻止其他master的对L1的访问。

CorePac内部内存保护模块(保护L1,LL2及XMC/MPAX)的寄存器被一个锁保护起来。默认情况下,这些寄存器没有被锁住,用户软件可以使用自定义的密钥锁住这些寄存器,然后,只有用该密钥进行解锁后才可以访问这些寄存器。

2.2 共享内存保护–MPAX

关于CorePac共享内存保护的基本信息参考“TMS320C66x CorePac User Guide(SPRUGW0)”中“扩展存储控制器(XMC)”章节;关于系统中其他master的共享内存保护基本信息参考“KeyStone Architecture Multicore Shared Memory Controller User Guide (SPRUGW7)”中“内存保护及地址扩展(MPAX)”章节。如下是例程中关于XMC/MPAX的配置样例,每一行代表MPAX中的一个分片配置。

逻辑地址低于0x0C00_0000 的地址访问不会进入XMC。对地址空间0x0000_0000~0x07FF_FFFF

进行访问时,在C66x CorePac内部进行地址解析。这块地址范围包括内部及外部配置总线,及L1D、L1P、L2存储空间。对位于0x0C00_0000~0x0FFF_FFFF区间的逻辑地址访问时,会经过L1 cache,并且在读操作时会经过预取缓存,与该地址范围对应的内存属性配置寄存器MAR是硬件拉死的,不可修改。也就是说对该逻辑地址空间的访问在进入XMC MPAX之前不会经过L2 cache,所以这块逻辑地址空间称为“快速SL2 RAM 路径”。对大于等于0x1000_0000的逻辑地址访问会首先经过L2 cache控制器,然后经过XMC MPAX,这种常规路径会增加一个cycle 的时延。

根据上述配置例子,在访问SL2时,采用逻辑地址0x0C00_0000的访问速率高于使用重映射后的逻辑地址0x1800_0000。但是0x1800_0000对应的内存属性寄存器MAR 是可编程的,因此可以配置通过0x1800_0000访问的SL2为non-cacheable及non-prefetchable。

注意替换地址RADDR是36-bit物理地址>>4。常见的DDR3错误配置如下:

或者

|