|

- UID

- 1023166

- 性别

- 男

- 来自

- 燕山大学

|

者:Djamel Haddadi,IDT公司

移动数据的爆炸式增长推动了通信基础设施新接收器体系结构的发展,以实现更大的容量和更高的灵活性。软件定义无线电系统将会成为下一代通信系统,该系统主要基于可以在天线侧进行采样,同时又支持大动态范围的高功效RF ADC。这类ADC采用非常先进的CMOS技术设计,使用时间交织(TIADC)体系结构获得了非常高的采样率。这一体系结构的缺点是时变失配误差,需要进行实时校准。本文介绍了一种新型的增益和时序失配误差背景校准方法,通过不太复杂的数字信号处理算法来实现这一方法。

双通道TI ADC失配误差

提高ADC速度一种有效的方法是两个ADC并行工作,不需要相位采样时钟。子ADC传输函数之间不可避免的微小失配会导致出现杂散谐波,大幅度劣化了实际动态范围。这种ADC有四类误差:DC失调误差、静态增益误差、时序误差和带宽误差。

在实际中,采用数字校准技术,DC失调误差处理起来比较简单。其中,带宽误差是最难处理的,一般需要通过谨慎的设计和布局来消除。本文中,我们将重点关注增益和时序误差校准,因为这是导致动态范围减小的主要因素。

建议的校准方法

在实际中,ADC的Nyquist带宽不会全部用掉,其中的一部分通常专门为抗混叠滤波器的滚降特性预留。这一空闲的频带可以被用于注入受约束的校准信号。校准信号使用正弦波,因为正弦波很容易生成纯净的频谱,这样有两个主要的特性可以被应用:

1. 振幅可以保持的足够小,以避免对动态范围有任何影响,同时提供了很好的估算精度。试验表明,-40 dBFS至-35 dBFS电平范围适用于14位ADC。

2. 频率限制在以下离散值上,以便降低数字信号处理算法的复杂度:

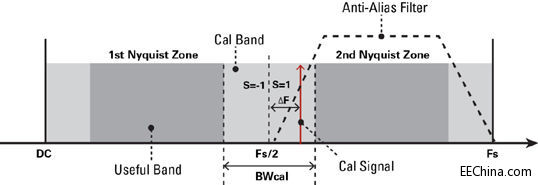

其中,Fs是TI ADC采样频率,P和K是无符号整数,S=±1,具体取决于校准信号相对于Nyquist区边沿的位置(参见图1)。校准信号可以很容易的在片上通过使用小数N分频PLL以ADC时钟作为参考信号来产生。选择足够高的K值,校准信号的谐波会在有用带宽之外混叠,这会降低滤波要求。在PLL输出采用可编程衰减器能够实现摆幅调整。

图1:频率规划显示了校准信号的位置。

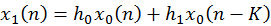

如果x0和x1表示两个子ADC的输出,而校准信号是其输入,可以使用公式1来表示它们,下面的表达式将这两路信号连接起来(忽略了噪声):

这一线性滤波公式的系数h0和h1可以明确地对应于增益g和时序Δt误差:

可以使用一阶近似,而设计中的失配误差比较小,将这一非线性方程组线性化并求逆。

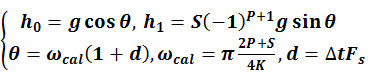

估算算法包括以下三个步骤:

1. 提取出校准信号,使用LMS算法,从子ADC的输出消除它,产生离散时间信号x0和x1。这一算法要求在校准频率上应用数字余弦/正弦参考信号。使用容量为4K (实际中,K<64)的小规模查找表(LUT)来产生余弦信号。通过简单的将余弦信号延时K来产生正弦信号。

2. 如图2所示,使用LMS算法,从提取出的x0和x1信号中自适应估算出系数h0和h1。

3. 从公式3中得到的线性方程组中计算出增益和时序误差。

图2:通过2抽头数字自适应滤波器进行增益和时序误差背景估算。

得到估算结果后,增益和时序误差被输入到数字校准引擎中。使用简单数字乘法器补偿增益。采用修正的小数延时滤波器对时序误差进行校准。通过多相和对称方法来降低滤波器实现的复杂度。估算和校准引擎都都以子ADC的采样速率运行,为进一步优化,估算模块还可以采用降采样的方案。

方法验证

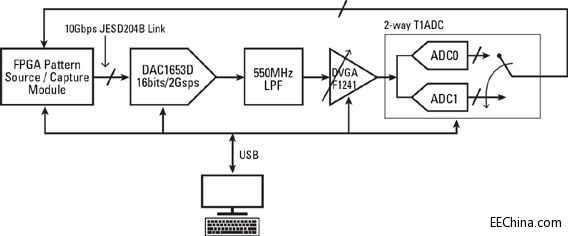

一路合成测试信号包括:中心是300 MHz的一路TM3.1、20 MHz LTE载波,以及一路253.44 MHz、-35 dBFS校准正弦波。对应于S=1、K=8、P=2K,可以使用图3中的测试设置来产生这些信号。这一设置具有低噪声和高线性度D/A转换器以及DVGA,因此,其动态范围非常高。我们采用了集成了高分辨率可调增益和时序误差功能的商用14位 / 500Msps TIADC。通过FPGA采集ADC原始数据,使用Matlab软件,由IDT校准算法处理这些数据。TI ADC的增益和时序误差分别被设置为大约0.5 dB和5 ps,以仿真最差情况。

图3:测试设置结构图。

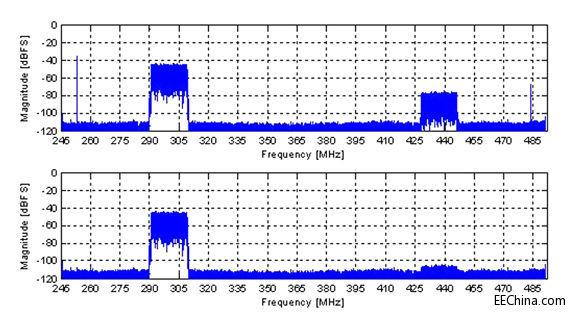

图4显示了校准前和校准后的数据功率谱。LTE载波镜像在校准前是-80 dBFS,校准后,降低了大约30 dB,达到-110 dBFS。提取和抵消算法完全消除了校准信号及其镜像。这一性能表现是在大约200 μs收敛时间内获得的。

图4:在校准之前(顶部)和校准后(底部)的功率谱,采用了300 MHz LTE载波。

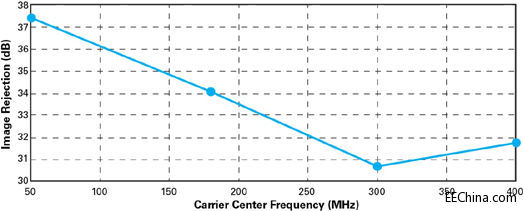

校准信号保持不变,LTE载波中心频率从50 MHz扫频到400 MHz,以便评估频率行为。如图5所示,得到的镜像抑制表明,在两个第一Nyquist区内,动态范围至少提高了30 dB。正如预期所示,如果带宽误差没有得到校准时,频率会受到限制,从而导致镜像抑制能力下降。

图5:镜像抑制和LTE载波中心频率对比,采用了固定校准信号。

结论

RF采样A/D转换器是下一代软件无线电系统的关键组成。利用时间交织体系结构可以获得非常高的采样率和低功耗,代价是动态范围劣化。从前文中可以看出,在使用带宽之外注入受约束校准信号,使用不太复杂的算法校准增益和时序误差,能够显著提高动态范围。对14/500 Msps原型的测量表明,两个第一Nyquist区的动态范围大约提高了30 dB。只要增益/时序失配误差模型保持有效,这一建议的方法可以用于速度更高的应用。

参考文献

[1] Jiangfeng Wu et al., “A 5.4Gsps 12b 500mW Pipeline ADC in 28nm CMOS”, 2013 Symposium on VLSI Circuits Digest of Technical Papers.

[2] Vogel, C.; Johansson, H., “Time-interleaved analog-to-digital converters: status and future directions,” ISCAS, May 2006.

[3] Laakso, T.I.; Valimaki, V.; Karjalainen, M.; Laine, U.K., “Splitting the unit delay,” Signal Processing Magazine, IEEE , vol.13, no.1, pp.30,60, Jan 1996

[4] IDTDAC1653D数据资料:

http://www.idt.com/document/dst/dac1653d-dac1658d-datasheet

[5] IDTF1241数据资料:http://www.idt.com/document/dst/f1241-datasheet |

|